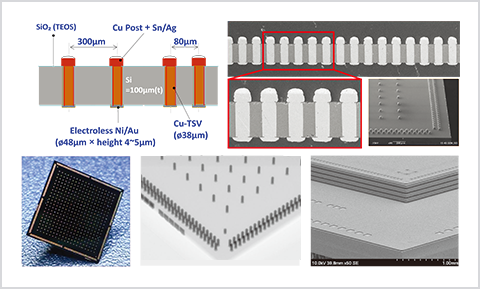

TSV(Through-Silicon Via)の製造工程、および各工程で使用するサムコの装置をご紹介します。

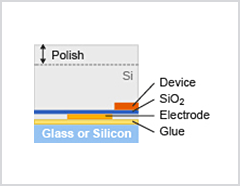

CMPによるSiの研磨

(Chemical Mechanical Polishing)

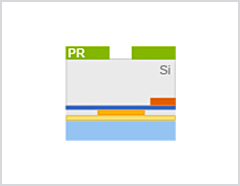

フォトリソグラフィー

貫通孔の形成

ボッシュプロセスによりSiをエッチングし貫通孔を形成

シリコン深掘り装置

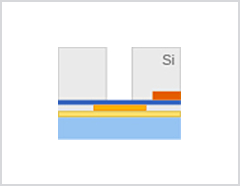

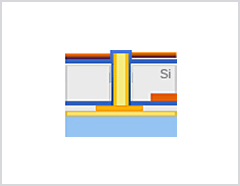

側壁への絶縁膜形成

貫通孔の側壁にTEOS-SiO2絶縁膜を形成

液体ソースCVD®装置

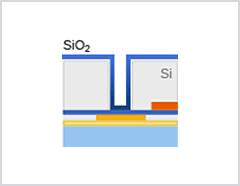

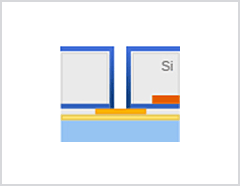

下部電極露出

電極上のTEOS-SiO2を選択的に除去

RIE装置

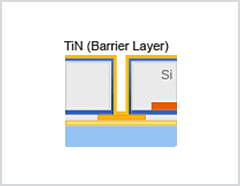

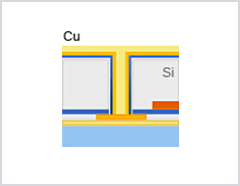

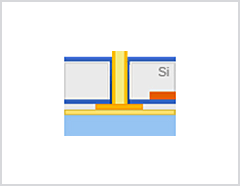

バリア層の形成

TiNバリア層によりCuの拡散を防止

メッキによる

Cuプラグの形成

CMP

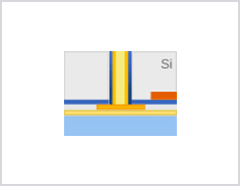

RIEによるCuプラグ出し

RIE装置

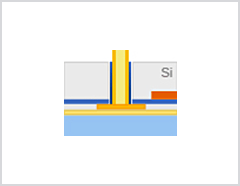

SiO2膜の形成

液体ソースCVD®装置

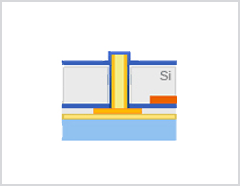

フォトリソグラフィー

SiO2膜のエッチング

RIE装置

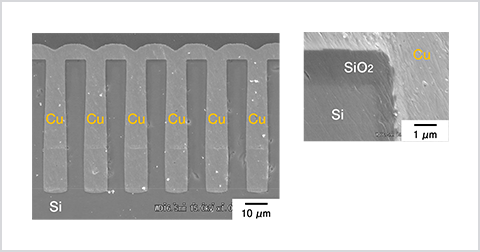

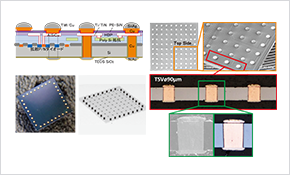

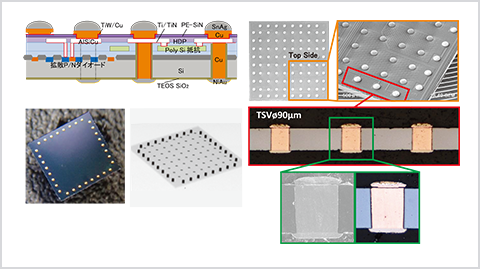

サムコ製装置における

TSVの作製事例

埋め込み特性

SIPスパッタによるシードCu膜厚:310nmの導入とめっき条件の最適化により低温プラズマCVD膜を1.36μm形成後でも高アスベクト比ビア(~7)への銅の完全充填が可能 。