## TSV向け低温形成絶縁膜技術

サムコは、LEDに続いてMEMS/TSV分野でも一貫生産ラインを提供する“SAMCO One Stop Solution”を提唱している。新製品『PD-330STC』は12インチウエハーへの成膜が可能であり、本格量産に対応可能となった。今回は3次元実装に不可欠なTSVへのサムコLS-CVD<sup>®</sup>装置ST-SeriesのTEOS-SiO<sub>2</sub>絶縁膜技術を紹介する。※LS-CVD<sup>®</sup>:Liquid Source CVD

### TEOSを用いたLS-CVD<sup>®</sup>装置ST-Seriesの特長

LS-CVD<sup>®</sup>装置とは、カバーレージ性に優れた液体ソースであるTEOSを用いた、サムコ独自のSiO<sub>2</sub>膜形成用プラズマCVD装置である。TEOSはSiH<sub>4</sub>に比べ非常に安全性が高く、自然発火性が無く、爆発性が低く、取り扱いが容易である。さらに、成膜にはカソード側の高いシース電界で得られるイオンエネルギーを利用しておらず、TSVのSiホール内壁に「低温」で「高カバーレージ」の絶縁膜を「高速」で成膜することができる。これらの特性はMEMS利用においても非常に重要である。

### 低温での高速成膜

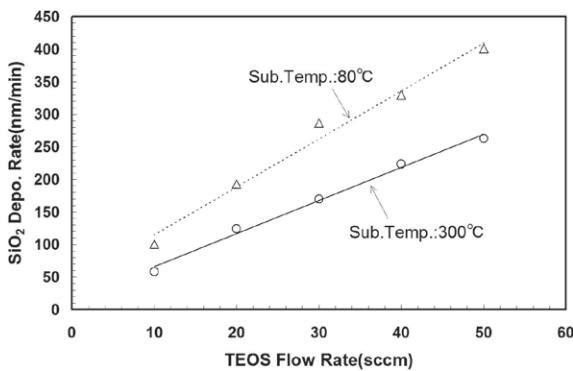

3次元実装の工程では、100μm程度まで研磨した薄いウエハーを用いる。このため、ウエハーを支持体に貼り付け処理することが多い。その際、樹脂接着材を用いるため、低温(150°C以下)での成膜が要求される。LS-CVD<sup>®</sup>装置では、バイアスで加速されたイオンアシストにより基板温度を下げても緻密な膜が形成できる。下図は成膜速度のTEOS流量依存性を記したものであるが80°Cの低温下で400nm/minの高速成膜が可能である。

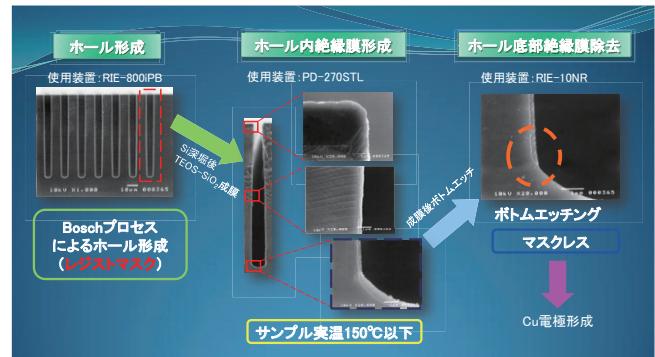

### 3次元実装加工工程

### SAMCO One Stop Solution

サムコの装置で以上のような成膜・加工が可能である。ホールサイズφ5μmでアスペクト比15のTSV Siホール内壁にカバーレージ性の高い絶縁膜を形成できている。現在のホールサイズはφ30～70μmでアスペクト比も最大5程度であるが、将来の高密度化にともない、貫通配線が更に微細化し、アスペクト比も大きくなることが予測される。

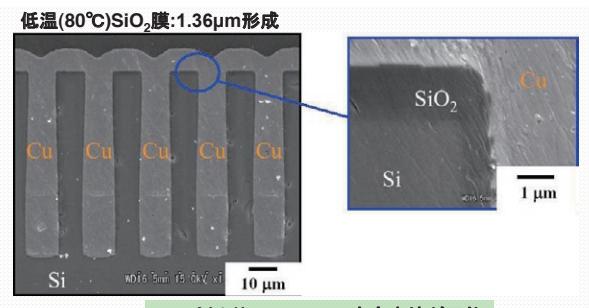

### 絶縁膜形成後のCu電極形成

～逆テーバーの難形状への埋め込み～

提供:大阪府立大学 化学工学分野

近藤和夫教授 齋藤丈靖教授

サムコのOne Stop SolutionでSiO<sub>2</sub>の絶縁膜を形成した後、Cu電極を形成したSEM写真である。Cuの完全充填ができるおり、また低温で成膜したSiO<sub>2</sub>は剥離・クラック等の問題は起きていない。

以上、サムコのTSV向け低温形成絶縁膜技術を紹介した。カバーレージ性の高い絶縁膜は多様な要求のあるMEMS分野にも応用できる技術である。