# PD-270STLCを用いた電子部品向けTEOS-SiO<sub>2</sub>成膜

【サムコ(株)開発部】

## ■はじめに

サムコでは従来より緻密かつ高成膜レートなTEOS-SiO<sub>2</sub>形成用LSCVD®装置として、光導波路、MEMS、TSV等の用途で、カソードカップリングプラズマCVD方式のPD-270STLCを提供してきた。今回電子部品用途向けに、良好な膜厚均一性及び安定性が得られたので紹介する。

## ■電子部品用途でのSiO<sub>2</sub>膜厚均一性の必要性

電子部品用途装置として、図1に成膜に用いるPD-270STLCの外観を示す。装置本体背面内部にTEOS供給系を2機設置し、TEOSを連続的に供給可能としている。トレイカセット方式を採用しているため、1トレイで基板サイズΦ4"以下であれば複数枚処理が可能である。また、1カセットにつき10トレイ連続での成膜処理が可能である。電子部品分野では一般的に、膜厚が均一で緻密なSiO<sub>2</sub>膜を用いられることが多い。特に、膜厚均一性は非常に重要であり、デバイス上での膜厚均一性は±1%以下を求められることが多い。サムコ独自のカソードカップリングプラズマCVD方式で成膜することにより緻密で良好な均一性を得ることが可能である。

## ■PD-270STLCでの成膜結果

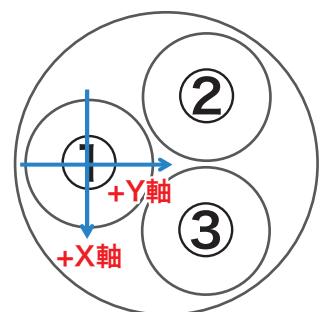

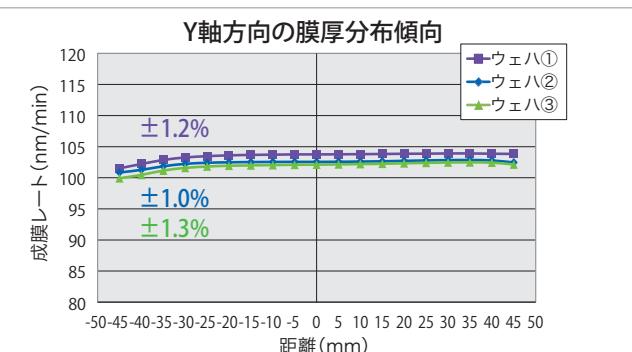

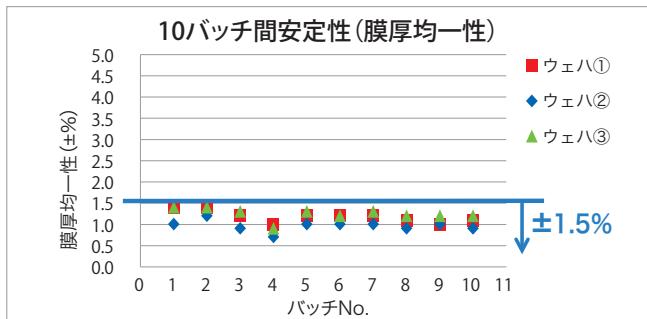

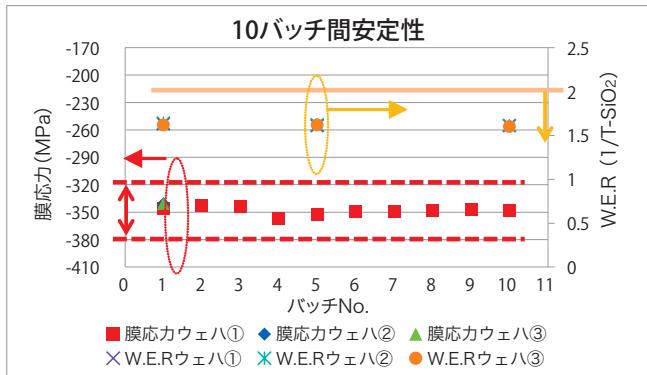

PD-270STLCで実施したTEOS-SiO<sub>2</sub>の1μmの成膜結果を以下に紹介する。図2にΦ4"×3枚置きでのウェハ配置と分布確認方向、図3にY軸方向の分布確認結果を示す。この装置ではトレイ上で同心円状の膜厚分布となるため、Y軸での分布が全体の膜厚均一性となる。図3よりSi基板上に成膜したSiO<sub>2</sub>膜の分布はY軸方向で±1.3%以下であり、良好な均一性が得られている。図4に10バッチ連続成膜結果を、図5に膜応力、ウェットエッチャレート(W.E.R.)のバッチ間均一性をそれぞれ示す。図4より、バッチ間の膜厚均一性は、Φ4"内で全て±1.4%以下であり、大きな膜厚分布の変動は発生していない。また、図5より、膜応力及びW.E.R.はほぼ安定しており、膜質も安定して成膜できていると考えられる。この膜厚均一性の条件で実際にΦ4"×3枚のデバイス基板上に成膜したところ、膜厚均一性はΦ4"内で±1%以下を達成している。また、10バッチ連続成膜でも同様の結果が得られている。

## ■終わりに

以上のように、PD-270STLCを用いた電子部品向けTEOS-SiO<sub>2</sub>成膜について紹介し、Φ4"×3枚上にて良好な膜厚均一性を得ることが確認できた。また、膜質においても再現性よく成膜可能である。この技術は電子部品分野に限らず他の様々な用途でも適用が可能と考えられる。

※LSCVD(LS = Liquid Source、液体ソースCVD)は当社の登録商標です。

図1 PD-270STLC外観図

図2 トレイ上のウェハ配置

図3 膜厚分布比較

図4 ウェハ面内バッチ間均一性

図5 膜応力、W.E.R.バッチ間均一性