# Ø6インチGaN系パワーデバイスの素子分離加工安定処理

サムコ(株) プロセス開発3部

## ■はじめに

窒化ガリウム(GaN)系半導体は、シリコン(Si)に代わる次世代パワーデバイスの材料として期待され、広いバンドギャップ、高い電子移動度などの優れた物性から炭化ケイ素(SiC)と共に研究・開発が進められてきた<sup>1)</sup>。信号の増幅を行う高周波デバイスや電力の制御・変換を担うパワーデバイス分野でGaN系半導体は既に実用化されており、市場はますます広がっている<sup>2)</sup>。特に、低ON抵抗、高チャネル移動度を要求されるGaN-HEMTはSi基板上に作製する手法が確立され<sup>3)</sup>、Ø6インチやØ8インチの基板を用いた生産が進められている。当社はGaN系発光デバイス用のICP-RIE装置およびCVD装置を提供しており、これらは研究開発から量産工程に至るまで広く利用されている。ICP-RIE装置のエッティング速度、面内均一性、連続処理時の安定性は、多くのユーザーから高い評価を頂いている。本レポートでは、量産対応のICP-RIE装置であるRIE-800iPCによるØ6インチSi基板に形成されたGaN系パワーデバイスの素子分離加工において、25枚の連続加工性を検証したので報告する。

図1. ICP-RIE装置

RIE-800iPC

## ■実験内容

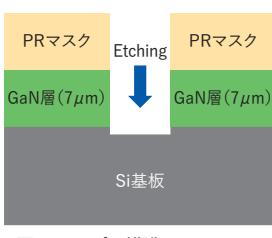

ICP-RIE装置RIE-800iPCを用いてØ6インチGaN層を形成したSi基板25枚の素子分離エッティングを行い、安定した量産プロセスの検証を行った。図1にRIE-800iPCの外観写真を示す。また、エッティングしたサンプル構造を図2に示す。Si基板上にGaN層(約7μm)が形成され、さらにフォトレジスト(Photoresist: PR)がマスクとして露光・現像されている。PRマスクの開口面積は10%程度である。素子分離加工はSi基板に到達するまでGaN層のエッティングを行うプロセスであるが、Ø6インチ全面でSi基板に到達している必要がある。そのため、プロセス上Si基板に対するオーバーエッティングが発生する。しかし過剰なオーバーエッティングはデバイスへのダメージや高さのばらつきによる後工程の加工精度悪化などの懸念がある。またウエハごとのGaN層の厚みにばらつきも存在する。そこでオーバーエッティング量を安定化させる目的として発光分光型のエンドポイントモニター(堀場製作所EV-140C)を使用した。

図2. サンプル構造とPRマスク

によるGaN層のエッティング

## ■実験結果

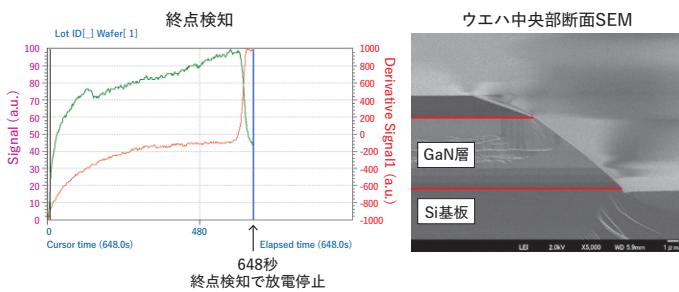

エンドポイントモニターによる終点検知を使用して1カセット25枚の連続処理を実施した。本実験で使用したウエハはGaN層が約7μmであり、その厚みはそれぞれ数%程度異なるものを用意した。終点検知

図3. 25枚連続処理の1枚目の終点検知による放電停止と断面SEMの結果

レシピによりSi基板に到達するまでエッティングが行われるため、エッティングレートが安定している場合、25枚の放電時間はGaNの膜厚に応じたものになる。終点検知による自動放電停止でオーバーエッティング量を制御した25枚連続処理の1枚目の測定結果とウエハ中央を走査型電子顕微鏡(SEM)で断面観察した結果を図3に示す。終点検知結果のグラフの緑線はN(窒素)、赤線はSiの発光強度を示しており、GaN層のエッティング終了後、Siの発光強度が増加し、信号が安定した648秒で放電が停止した。また、断面SEMの画像からもGaN層をエッティングしきってSi基板への到達が確認できた。

次に、エッティングの面内均一性とエッティングレートの安定性を評価するため、1枚目、13枚目、25枚目のウエハを抜き出して触針段差計によるエッティング深さ測定とエッティング時間からのエッティングレートを算出した。結果を図4に示す。

|                    | 1枚目    | 13枚目   | 25枚目   |

|--------------------|--------|--------|--------|

| Time [s]           | 648.0  | 652.5  | 644.4  |

| 9点平均深さ [μm]        | 7.29   | 7.31   | 7.27   |

| エッティングレート [nm/min] | 675.0  | 672.2  | 676.9  |

| 面内均一性              | ±2.32% | ±1.99% | ±1.90% |

| エッティングレート均一性       | ±0.35% |        |        |

図4. ウエハ1枚目、13枚目、25枚目の面内均一性とエッティングレート確認結果

1枚目、13枚目、25枚目の3枚についてはウエハ外周5mmを除く9点で段差測定しており、エッティングレートは平均で675 nm/min、面内均一性は<±3%、ロット内のエッティングレート均一性は±0.35%であり、25枚連続処理での安定性が確認できた。

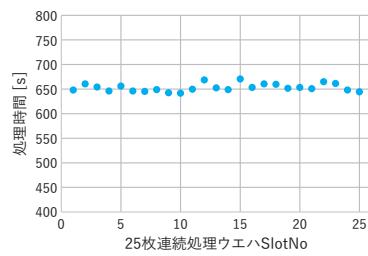

最後に、25枚すべての放電停止時間を図5に示す。放電時間は641~670秒の範囲であり、ばらつきは±2.2%であった。前述の通りエッティングレートは±0.35%と安定しているので、放電時間のばらつきはGaN膜厚のばらつきに起因すると推測される。このことから、GaN膜厚が数%異なるウエハに対しても、オーバーエッティング量を制御できるエンドポイントモニターの有効性が確認できた。

図5. 25枚連続処理の放電停止時間

## ■おわりに

本レポートでは、量産対応のICP-RIE装置であるRIE-800iPCを用いたGaN系パワーデバイスの素子分離加工技術と、その優れた安定性について紹介した。高いプロセス再現性とエッティング面内均一性を持長とするRIE-800iPCは、GaN系半導体のエッティングはもちろん、GaAsやInPなどの化合物半導体、SiO<sub>2</sub>やSiNといったSi系材料、さらにPZTやPtなどの強誘電体や金属材料、ポリイミドなどの樹脂材料まで、多種多様な素材の加工に対応可能である。

当社は次世代デバイス向けプロセス技術の開発を積極的に推進し、お客様の量産工程における安定性課題の解決と品質向上に貢献していく。

1) 須田淳、堀田昌宏、鐘ヶ江一孝“GaN 縱型パワーデバイス実現に向け得た点欠陥評価”応用物理 Vol90, No10(2021):628-631

2) Yusuke Kumazaki 1,2\* Over 80% power-added-efficiency GaN high-electron-mobility transistors on free-standing GaN substrates: Applied Physics Express 14, 016502 (2021)

3) Si基板上へのGaN単結晶の成長とデバイス応用 応用物理 第81巻 第6号(2012)