# 原子層レベルのエッチング制御、 Atomic Layer Etching装置の紹介

サムコ(株) 技術開発統括部

プロセス開発3部

## ■はじめに

半導体デバイスの微細化・高集積化に伴い、エッティングプロセスにおける原子層レベルでの制御が求められている。その中で原子層エッチング(Atomic Layer Etching: ALE)が注目されている。ALEは改質と除去工程を交互に繰り返すサイクルプロセスで構成され<sup>1)</sup>、それぞれで自己律速反応が起きる<sup>2)</sup>。改質工程では、エッチャントが基板表面に吸着し、1原子層のみ反応し改質層を形成する。この反応は自己律速的に進行し、それ以上は反応しない。除去工程では、改質された層のみがエッティングされ、基板と未反応の原子はエッティングされない。

2つの自己律速反応により、1サイクルで除去される原子層の厚みは一定となり、以下の特徴を有する。

## 1. 高精度な深さ制御

1サイクルあたりのエッティング量が数Å単位で一定であるため、非常に高精度な深さ制御が実現できる。

## 2. 低ダメージ

イオンエネルギーが低く、基板ダメージや欠陥の発生を最小限に抑えることができる。

## 3. 高均一性

ウエハ全面で均一なエッティング深さが実現され、高いプロセス再現性が得られる。

以上の特徴から、ALEはFin FET、3D NAND、パワーデバイス、化合物半導体など、最先端デバイスの製造に利用されている。ALEには、Plasma ALE、Thermal ALE、Plasma-thermal ALE等の方式がある<sup>3, 4)</sup>。当社では、それぞれの方式に関して幅広く研究・開発を行っている。本稿では当社ALE装置の特徴、ならびにプロセスデータについて述べる。

## ■ALE装置

当社は、従来のICP (Inductively coupled plasma) エッティング装置にALE機能を追加しており、1台で両方のエッティングを行うことができる。ALE装置は以下の2つの特徴を備えている。

### 1. 低Bias出力の精密制御

当社のシステムではBiasの高周波伝送ラインにアッテネータと切り替えスイッチを搭載している。ALEでは、自己律速状態を実現するために非常に低い出力領域でのBias制御が求められ、材料ごとに異なる最適な制御領域を実現する必要がある。アッテネータの搭載により、低出力域におけるBias出力の高精度な制御が可能になる。さらに、当社ではアッテネータだけでなく、電力計によるBias出力管理により制御性を向上している。

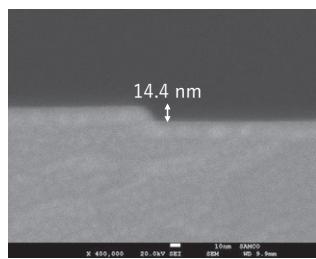

図1. ALEによるGaN/AlGaNエッティング SEM像 (500 nmトレーナー幅)

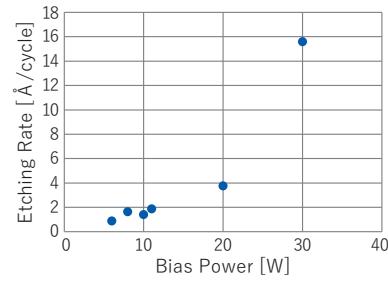

図2. Bias出力とGaN/AlGaNエッティングレート

## 2. ガス導入応答性の向上

反応室へのガス導入応答性を向上するため、ALE用のガスボックスを反応室近傍に配置している。ALEでは改質と除去工程でガスを入れ替えるため、ガスの切り替え導入時間の短縮がスループット向上において重要となる。ガス切替時間は、ガス配管の長さとバルブ応答時間に強く依存するため、配管構成を短くすることでガススイッチング応答を高速にし、改質の再現性を保ちつつサイクルタイムを短縮させている。また、ALEに類似したプロセスではあるが自己律速反応にならないQuasi ALEでは、改質工程(堆積工程)のエッチャントの堆積厚さが1サイクルのエッティング深さを決定するため、ALEと比較して高精度なガススイッチング応答が必要である<sup>5)</sup>。

## ■プロセスデータ

Ø6インチのポリイミドテープ付き熱酸化膜Siウエハ上にGaN/AlGaN構造のチップサンプルをオイルにて貼り付け、ALE処理を実施した。改質にはCl<sub>2</sub>ガス、除去はArガスを使用した。

図1にエッティング幅500 nmのトレーナー形状をALE処理し、マスクであるSiN膜を除去したサンプルSEM像を示す。88 cycleのALEにてエッティング深さ14.4 nmとなった。エッティングレートは1.63 Å/cycleであり、原子層レベルのエッティング量となっている。

図2にBias出力を変更し1 cycle当たりのエッティングレートを測定した結果を示す。Bias出力6～11 Wは同程度のエッティングレートを示しており、ALEの自己律速性が成立していると考えられる。

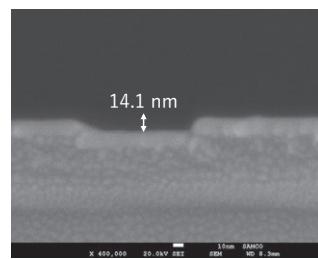

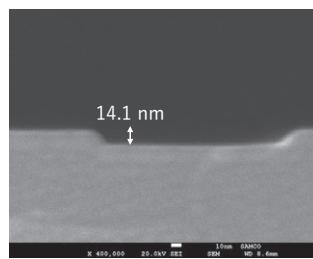

図3に500 nm幅トレーナーと同じ条件で100 nm幅および200 nm幅のトレーナーを処理した結果を示す。異なるパターン幅でもともに深さ14.1 nmとマイクロローディング効果を防ぎ優れた深さ均一性が得られた。

## ■おわりに

本稿では、原子層レベルでのエッティングが可能なALE装置の特徴と、プロセスデータを紹介した。ALEは従来のICPエッティングでは困難であった原子層レベルのエッティング制御やダメージ低減において優位性を持つ。今後、ダメージやデバイス特性評価についても紹介していく。

＜謝辞＞ 本稿に掲載しているSEM像は、名古屋大学様からご提供いただいたサンプルを使用しています。心より感謝申し上げます。

- 1) Keren J. Kanarik, et al., "Overview of atomic layer etching in the semiconductor industry" Journal of Vacuum Science & Technology A 33, 020802 (2015)

- 2) Satish D. Athavale, et al., "Realization of atomic layer etching of silicon" J. Vac. Sci. Technol. B 14(6), Nov/Dec 1996

- 3) Xia Sang et al., 2020, "Physical and chemical effects in directional Atomic Layer Etching" Journal of Physics D: Applied Physics

- 4) J.W. Daulton, et al., "Selectivity Control in AlGaN/GaN Atomic Layer Etching" AVS ALE Workshop 2015

- 5) Sonam D. Sherpa et al., "Quasi-atomic layer etching of silicon nitride", Journal of Vacuum Science & Technology A 35, 01A102 (2017)

(a) 100 nmトレーナー幅

(b) 200 nmトレーナー幅

図3. トレーナー幅の異なるGaN/AlGaNのALEエッティング SEM像