# トレンチMOSFETのゲート形成に必要な成膜技術の紹介

【サムコ(株) 基盤技術研究所】

## ■はじめに

炭化ケイ素(SiC)や窒化ガリウム(GaN)は、その物性からパワーデバイス市場においてSiに代わりうる材料として期待されている。SiCに関しては、昇華法の発展によりSiC基板の入手が容易になったことからSBDやMOSFET等のデバイス開発が加速し、モジュール化も進められている。MOSFETでは、低損失化を目的にさらなる低オン抵抗化、高耐圧化に向けた開発が行われている。特にトレンチMOSFETは一部で実用化されており、SJ-MOSFETやIGBT等の研究開発が行われている。GaNに関しては、今後数年以内にNaフラックス法等の進歩によりGaN基板の入手が容易になり、かつイオン注入等によるp・nタイプの生産が可能になり、実用化が加速すると予測している。いずれの材料においてもトレンチゲートが重要であり、トレンチ加工、ゲート酸化膜形成および電極形成は必須の要素技術である。当社はこれまでSiC、GaNのトレンチ加工技術に関する取り組みを続けている。<sup>[1,2]</sup> ここでは高耐圧化のためのトレンチ部へのゲート酸化膜の成膜およびゲート電極としてのタングステンの成膜について紹介する。

## ■トレンチ構造に適したゲート酸化膜の成膜と評価

SiC、GaN系のトレンチMOSFETでは、逆バイアス印加時にトレンチ底面角部のゲート酸化膜に電界が集中し破壊するという課題がある。一般的には、トレンチ底部をラウンド形状にすることにより電界集中を緩和している。当社では、この課題を解決する方法としてトレンチ側壁(MOSゲート部、SiO<sub>2</sub>:~50nm)の膜厚は薄く、トレンチ底面の膜厚は厚くした酸化膜を形成することを提案する。当社のカソードカッピングタイプのPECVDによるSiO<sub>2</sub>成膜では、トレンチ側壁より底面の膜厚を厚くすることが可能である。つまり、酸化膜の耐圧を利用するこの方法によりデバイスの高耐圧化を実現できる。しかし、プラズマがSiC表面に与える影響(一般的にプラズマダメージ)によって界面準位密度が高くなる懸念がある。そこでSiO<sub>2</sub>/SiC界面に関しては、低界面準位、低オン抵抗を達成すべく新しいAtomic Layer Deposition(ALD)を提案する。

当社では、ALDで成膜したSiO<sub>2</sub>膜(ALD-SiO<sub>2</sub>、プラズマレス)とPECVDで成膜したSiO<sub>2</sub>(PECVD-SiO<sub>2</sub>)の積層膜によるゲート酸化膜の形成を試みた。形成後アニールを行い、MOSキャパシタとトレンチ型SiC MOSFETを試作し、ゲート酸化膜の性能評価を行った。

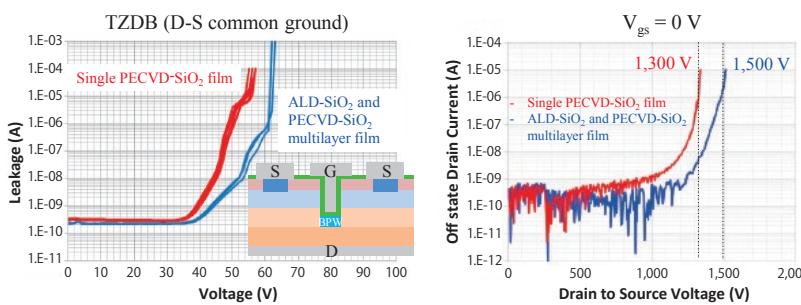

積層膜によるゲート酸化膜は、デバイスとの界面にALD-SiO<sub>2</sub>膜(SAMCO AL-1使用)をトレンチ側面に20nm、その上にPECVD-SiO<sub>2</sub>膜(SAMCO PD-270STL使用)を30nmの合計50nm成膜した。また、比較のためPECVD-SiO<sub>2</sub>膜のみでトレンチ側面に50nm成

膜したゲート酸化膜を作製した。トレンチ底面の厚さは、ALD-SiO<sub>2</sub>膜とPECVD-SiO<sub>2</sub>膜の積層膜が138nm、PECVD-SiO<sub>2</sub>膜のみが173nmであり、いずれも成膜後にポストアニールを行っている。

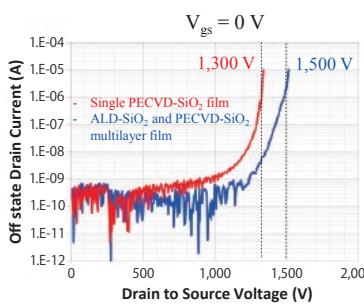

図1にTZDB法によるトレンチ型SiC MOS構造のゲート酸化膜の絶縁破壊電圧を示す。図1より算出したトレンチ側面のALD-SiO<sub>2</sub>膜とPECVD-SiO<sub>2</sub>膜の積層膜とPECVD-SiO<sub>2</sub>膜のみのそれぞれの絶縁破壊強度は11.2 MV/cmと10.0 MV/cmであった。また、図2にオフ状態でのトレンチ型SiC MOSFETの耐圧測定結果を示す。ALD-SiO<sub>2</sub>膜とPECVD-SiO<sub>2</sub>膜の積層膜は耐圧が1,500Vと良好な結果であり、トレンチ底面の酸化膜の膜厚が薄いにも関わらずPECVD-SiO<sub>2</sub>膜の耐圧値1,300Vよりも優れた特性を示した。この結果から、ALD-SiO<sub>2</sub>膜をPECVD-SiO<sub>2</sub>膜とデバイス界面の間に成膜することで、界面準位密度が低減されたことが示唆される。

## ■熱CVDによる金属ゲート電極の形成

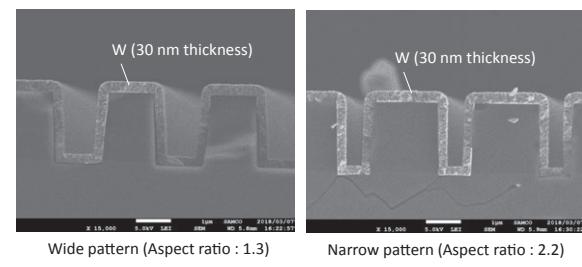

高融点金属であるタングステン(W)は、パワーデバイスのコンタクト電極として期待されている。また、タングステンは低抵抗でかつゲート酸化膜との界面での空乏化が発生しないためPoly-Siに比べて優れており、SiCやGaN系のパワーMOSFETのゲート電極としても期待されている。トレンチ構造への適用を検証するためにモノシリコンとWF6およびH<sub>2</sub>を用いた熱CVDによるタングステンの成膜を試みた。

プラズマCVD装置SAMCO PD-220Lを熱CVD用に改造して成膜した。トレンチ幅の違う2種類のパターンに膜厚30 nm狙いでタングステンの成膜を行った。成膜結果を図3に示す。図3より、表面の凹凸が少ない滑らかな膜がカバレッジ性よく成膜できていることが確認できた。成膜時間を調整することでトレンチへの埋め込みも可能になると想定しており、ゲート電極としてだけではなくコンタクト電極の形成にも応用できると考えている。

## ■おわりに

トレンチMOSFETのゲート形成に必要なゲート酸化膜の成膜と金属ゲート電極の成膜について新たな提案を行い、特性やカバレッジ性を確認した。また、当社ではSiCやGaN系のトレンチMOSFETの作製に必要不可欠なエッチングについても技術の蓄積があり、開発を行っている。

## ■参考文献

- [1] Samco NOW vol.104 Technical-Report, 2019年1月

- [2] Samco NOW vol.105 Technical-Report, 2019年4月

図1 2種類のゲート酸化膜の絶縁破壊電圧測定

図2 オフ状態 ( $V_{gs} = 0$  V) でのトレンチ型SiC MOSFETの耐圧測定

図3 トレンチ構造へのタングステンの成膜