# パワーデバイス用GaNのトレンチ加工

【サムコ(株) 開発部】

## ■はじめに

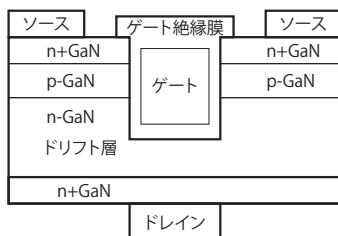

GaN系半導体はその物性から4H-SiC、 $\beta$ -Ga<sub>2</sub>O<sub>3</sub>等と並びパワーデバイス材料として期待されている。現状、GaN基板は高価なことから、SiC基板、サファイア基板、Si基板上にデバイス構造をエピタキシャル成長させたプレーナー型のデバイス、例えばHEMT、MOSFETが開発され、既に中電力、高周波用途として実用化に至っている。最近ではNaフラックス法、HVPE法等の基板形成技術の発展に伴いGaN基板を用いた研究発表も盛んになってきている。今後数年以内に高耐圧、低ON抵抗、高チャネル移動度を兼ね備えたトレンチMOSFETが実現すると予測している。図1にトレンチMOSFETの例を示す。

弊社は半導体製造装置メーカーとして、GaN系発光デバイス製造におけるICPエッティング装置、CVD装置及びプロセス技術を提供してきた実績がある。また、4H-SiCパワーデバイスに対してもトレンチ加工、メサ加工等に対応できる装置を提供している。

今回、これまでの加工実績をベースにGaNのトレンチ加工を行ったので紹介する。

図1. トレンチMOSFETの模式図

## ■GaNのトレンチ加工

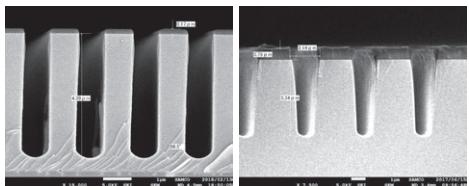

数  $\mu$ mのGaNトレンチエッティングの結果を図2に示す。サファイア基板上にGaNをエピタキシャル成長させた試料を用い、ICPエッティング装置はサムコ製RIE-400iPを使用した。図2の写真に示すように、トレンチ部は垂直形状であり、底部は凹型（ラウンド）形状となっている。また、順テーパー形状についても研究開発を進めており、これらの形状はRIE-400iPのエッティング条件調整により制御している。

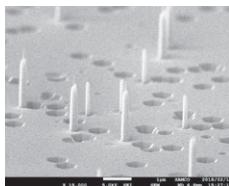

このように当社が開発してきたGaN系発光デバイスのエッティング技術を応用することできれいなトレンチ加工は可能であるが、トレンチ加工においてエッティング面の平坦性を得るために、GaNの結晶欠陥に特に注意しなければならない。サファイア基板上にヘテロエピタキシャル成長させたGaNエピ層は製品によって異なるが、その結晶欠陥密度は $10^7 \sim 10^8/cm^2$ 程度と報告されている<sup>1)</sup>。図3に結晶欠陥を起点として生じるエッティング底面の例を示す。弊社ではプロセス技術により図2で示したような平滑なエッティング形状を実現しているが、エピ層から結晶欠陥が減少すれば加工形状、エッティングレート等のプロセスウインドウを広げることができる。

図2. サファイア基板にエピタキシャル成長させたGaNのトレンチエッティング

図3. 結晶欠陥が生じた表面のSEM像

また、結晶欠陥の存在はエッティングだけでなく、リーク電流、耐圧、信頼性等のデバイス性能にも影響する<sup>2)</sup>。デバイス性能を向上させるため、及びそれを実現させるためのプロセス技術、プロセスウインドウの両面から見て、ヘテロエピタキシャル成長における結晶性の向上は不可欠であり、最終的にはGaN基板上に良質な結晶をエピタキシャル成長させることになる（GaN on GaN）。

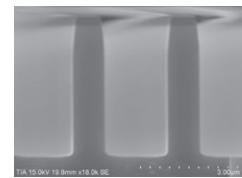

GaN on GaNは近年技術開発が進められている<sup>3)</sup>が、基板が高価であり技術革新が求められている。今回その  $\phi 4"$  GaN on GaNをエッティングした結果を報告する。図4にGaN on GaNトレンチエッティングのSEM像を示す。垂直形状で底部はやや凹型の平坦であり、エッティングレート：500nm/min、ウェハ面内均一性  $\pm 4\%$ 以下であった（表1）。ゲートが形成されるトレンチ部に求められる形状は、壁面の垂直性及び平滑性と、底面のラウンド形状が挙げられるが、これらはチャネル移動度、ゲート電流及び耐圧特性に関係する。弊社では今後もより実用性を高めたエッティング形状を開発する予定である。また、トレンチ加工後にKOH、TMAH等のアルカリ水溶液による平滑化処理を行うことも有効と考えている。

図4. GaN on GaNトレンチエッティング

表1. エッティング結果

|                      | エッティングレート | 面内均一性     |

|----------------------|-----------|-----------|

| $\phi 4"$ GaN on GaN | 500nm/min | $\pm 4\%$ |

## ■最後に

弊社は、GaN-LEDの開発初期段階より長年取り組んできたGaN系半導体のエッティング技術の蓄積があり、多くのお客様のさまざまなニーズに応えてGaN-HEMTのリセスエッティングやGaN/AIGaNの高選択比エッティングを提供してきた。今回はGaNトレンチエッティングについて良好な成果を得た。今後もプロセスを改善してGaNトレンチMOSの実用化に役立つプロセスを開発していく予定である。また、エッティングだけでなくゲート酸化膜形成を目的としたALD、CVDや、メタルCVDの開発も進めており、GaN系パワーデバイス向けのトータルソリューションを提供していく。

## ■謝辞

本報告の写真を掲載するにあたり、提供頂いた産業技術総合研究所に感謝の意を表します。

## ■参考文献

- 1) サファイア基板上GaNの成長に関する研究、極微構造デバイス研究センター報告書、5巻1-112、名古屋工業大学極微構造デバイス研究センター

- 2) 天野浩：短波長可視・紫外発光デバイス開発と半導体ヘテロエピタキシー、71,1329、応用物理

- 3) 皿山正二：真のバルクGaN単結晶の必要性と研究開発動向、Science & Technology Trends、科学技術動向研究