# トレンチ型SiC MOSFETの実現に向けた取り組み

[サムコ(株) 基盤技術研究所]

## ■はじめに

ワイドバンドギャップ半導体である4H-SiCは、半導体の主流であるSiと比較すると、高耐圧や熱伝導などの優れた物性を有している。このため、4H-SiCは小型化、省エネ化が進むパワーデバイス用材料として研究開発が進められてきた。現状、デバイス開発とともに車載、電源等への実用化に向けた開発が進められている。4H-SiCパワーデバイスの一例としてMOSFET (Metal Oxide Semiconductor Field Effect Transistor) があり、Siでは実現が難しい「高耐圧」、「低オン抵抗」、「高速スイッチング」を同時に実現できる。MOSFETには更なる高効率化のために、例えば更なる低オン抵抗化が要求されており、トレンチ型MOSFETはこの要求を実現することができる素子として開発が進められている。当社では、トレンチ型SiC MOSFETの製作工程で必要なドライエッ칭によるトレンチ加工、ALDとPECVDによるゲート絶縁膜の形成などの開発を行っている。ここではトレンチのエッ칭結果に加えて当社のALDとPECVDで成膜したゲート絶縁膜に関して紹介する。

## ■SiCトレンチエッ칭結果及びゲート絶縁膜の成膜結果

SiCトレンチエッ칭では、高エッ칭レート、高選択比 (SiC/SiO<sub>2</sub>)、トレンチ側壁の平滑性、トレンチ底部のラウンド形状、トレンチの垂直性が要求されている。

現在、4H-SiC基板はφ4インチもしくはφ6インチが主流である。当社ではφ4インチ用、φ6インチ用装置として「RIE-400iP/400iPC」、「RIE-800iP/800iPC」を販売している。両装置とともに、エッ칭レートは450nm/min以上、選択比は5以上、エッ칭深さの均一性は±3%以下を達成している。また、側壁平滑性やトレンチ形状(垂直性・ラウンド)も要求を満たす結果が得られている。図1にRIE-800iPによるSiCトレンチエッ칭例を示す。

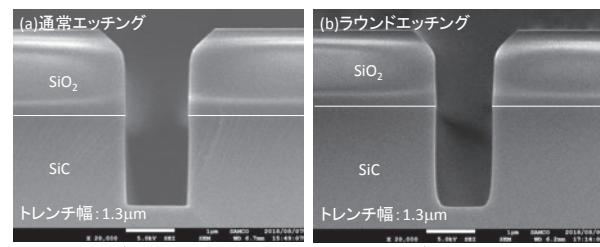

ゲート電極を形成する際にトレンチ底部に角の部分が存在すると、電圧を印加した際に電界集中が生じ、ゲート絶縁膜が破壊されてしまうという問題がある。そのため、エッ칭後は1500°C前後でアニールを行うことで、トレンチ底部をラウンド形状にする場合がある。当社では、アニール工程なしでトレンチ底面エッジ部をラウンド化するトレンチエッ칭プロセスを開発した。このエッ칭結果を図2に示す。

今後はラウンド形状の更なる最適化やトレンチ幅に応じたエッ칭条件の最適化など、ユーザーの要求に応じて対応していく。

図1 RIE-800iPによるSiCトレンチエッ칭例

## ■SiCトレンチ構造へのゲート絶縁膜の形成

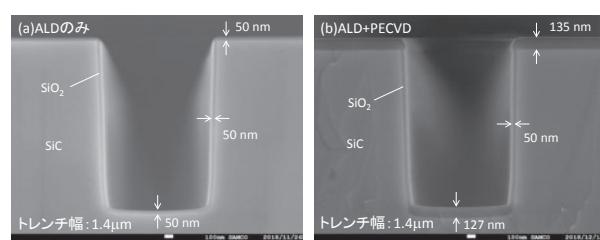

トレンチ型SiC MOSFETでは電流の流れるトレンチ側面のゲート絶縁膜は薄く、トレンチ底部のゲート絶縁膜は耐圧を持たせるために厚くしたい。一般的にSiCパワーデバイス用途のゲート絶縁膜として、ALDやPECVDで成膜したSiO<sub>2</sub>膜が用いられる。ALDで成膜した膜はPECVDで成膜した膜よりも耐電界強度が高く、CV特性のヒステリシス性が小さい(1V程度)利点があるが、トレンチ側面と底面に均一に成膜されてしまう。一方、当社のカソードカッピングリングタイプのPECVDで成膜した膜はトレンチ底部を厚くできる。CV特性のヒステリシス性はポストアニールで解決できる。

そこで、当社はデバイスとの界面付近のみALDでSiO<sub>2</sub>を成膜し、その上にPECVDでSiO<sub>2</sub>を成膜した積層膜によるゲート絶縁膜の形成を試みた。このゲート絶縁膜を評価するために、トレンチ型SiC MOSFETを作製し、デバイス特性評価を行ったところ、耐電界強度は10MV/cm以上、オフ状態(V<sub>g</sub>=0V)でのドレイン・ソース間耐圧は約1500V等の良好な結果が得られた。図3にSiCトレンチへのSiO<sub>2</sub>の成膜結果((a)ALDのみ、(b)ALD+PECVD)を示す。

## ■おわりに

今回はトレンチ型SiC MOSFETの製作に必要なSiCトレンチエッ칭とゲート絶縁膜の形成について紹介した。更にトレンチ型SiC MOSFETの製作には上記以外にも様々な工程が必要であり、当社の装置でSiCトレンチエッ칭用SiO<sub>2</sub>マスクの成膜及びエッ칭、Poly-Siゲート電極やAl電極のエッ칭なども可能である。当社では装置性能の更なる向上やプロセスデータの蓄積により、4H-SiC、またGaN、β-Ga<sub>2</sub>O<sub>3</sub>を含めパワーデバイス分野の発展に貢献していく。

図2 SiCトレンチの底面エッジ部ラウンド化

(a)通常エッ칭、(b)ラウンドエッ칭

図3 SiCトレンチへのSiO<sub>2</sub>の成膜 ((a)ALDのみ、(b)ALD+PECVD)